近年来,芯片一直是业界探讨的热点话题。不过,5G基站芯片相对“神秘”,除了部分设备厂商公布先进的7nm/5nm基站芯片研发进展,整体来说并没有引起过多的关注。

今日,在中国移动2022科技周暨移动信息产业链创新大会上,中信科移动技术总监冯亮发表演讲,介绍了5G基站芯片的发展现状,以及5G小站的演进思路。

工艺十分广泛

根据冯亮介绍,5G基站芯片范围广泛,包括CPU、FPGA、交换芯片、电源芯片、时钟芯片等等。与智能手机等消费品追求顶尖工艺有所不同,5G基站作为工业品,对芯片工艺的整体要求并不高,不同的芯片采用各自适应的工艺。

从应用现状来看,核心的CPU、FPGA、DFE(数字前端)等核心芯片对工艺要求较高,主要采用10nm到28nm的工艺。TRX、DDR4、交换芯片等重要芯片,采用19nm到28nm工艺。而一些配套器件、通用器件,采用一些非常成熟的工艺即可。

常规器件的工艺要求很低,可以全环节自主可控;而工艺要求高的核心器件,抗风险能力弱,需要广泛的设备厂家支持。冯亮指出,这需要业界联合对核心器件群培育,降低单一供货厂家的风险,拉动5G基站芯片全产业链提升。

目前,中国移动牵头成立了信息通信芯片产业链创新中心,其中就有一个芯片联合攻关工作组。该中心参与厂家包括大唐、中兴、华为、京信、联想等设备商,以及大量芯片厂商,汇聚产业资源,推动5G基站芯片开发。

核心器件分析

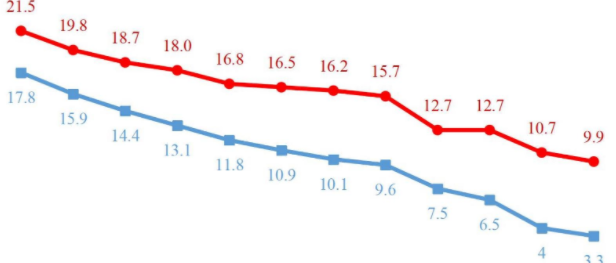

冯亮对国内企业5G基站芯片的竞争力进行了分析。其中,CPU、FPGA和基带SoC,国际来看,目前在商用市场用途广泛,成本、功耗和竞争力具有优势,普遍的问题是对本土支持和响应速度偏弱。据悉,部分厂家将推出5nm及更尖端工艺的芯片。国内来看,整体能力和集成度相对国际产业存在差距,并拉大功耗和成本差距。同时,入局者众多,可有效抵御供应风险。

冯亮介绍,基站商用产品数字器件工艺要求等级高,目前集中在16nm及以上工艺,高端CPU芯片和高端FPGA芯片已用到10nm工艺,而国内产业高端CPU芯片当前是14nm工艺,高端FPGA工艺还在28nm。

基站商用产品模拟器件的工艺要求等级低于数字器件,国外高集成度的射频收发器件采用28nm工艺,最新的在向16nm突破:国内产业射频收发器件采用的是28nm工艺。

此外,小功率功放芯片使用GaAs材料的功放,目前衬底基本都是进口,国内产业研究所有研发,处于刚起步阶段。其他低集成度器件采用90nm及更低工艺等级器件全环节自主可控,已在商用基站产品批量使用。

5G小站演进思路

在演讲中,冯亮也谈到了5G小站的演进思路。随着运营商5G扩展型小基站集采临近,5G小站即将迎来规模化商用,5G小站平台的产品成本和功耗是制约未来发展的关键,底层芯片自主可控方案对于小站技术演进和产业链战略安全,具有重要意义。

5G小站BBU的演进方向是通用器件向专用器件发展、分立式器件向一体化器件发展,网络处理单元 (NPU)、物理层处理单元 (PHY)等关键单元是重点突破方向。

pRRU方面,面向室内覆盖场景的5G pRRU产品对芯片低功耗和低成本要求较高,国内产业芯片的产品序列、性能指标、应用经验等方面尚有差距,亟待提升,数字前端芯片、射频集成收发器等关键器件是重点突破方向。

中国信科同国内产业多家芯片厂家保持沟通,开展低功耗和低成本小站研发。目前已完成立项和前期预研、进入总体方案设计阶段,预计2022年末推出低功耗、低成本的小站样机。